Happy new year to you too!

From memory it was a single pulse with one ADC starting on the falling edge and the other starting on the rising edge. The pulse width is then used to stagger their start times. That was two years ago, so I may be mis-remembering, but there are details here. You’ll see I also plumb the timer output to a spare external pin for scoping/debugging, so you could potentially do that to find out what’s going on. If you want them to start at the same time, you should configure both ADCs to start on the same edge - falling or rising, doesn’t matter.

Multiple pulses? It shouldn’t do. Those edges are just used to start the ADCs running. Once started they run forever and ever and ever… in the spirit of “let no mains cycle go unmeasured”.

If I’m reading your scope trace correctly that’s about 640nsecs between starts, and you’re running the core at 120MHz? That might be the time of two back-to-back calls to HAL_ADC_Start_DMA() - which would suggest they’re set to “triggered by s/w” instead of “triggered by timer edge”. Is the 640nsecs consistent? One way to test that theory would be to put a bit of code between the two calls - nothing substantial (so not a call to HAL_Delay()) but maybe just toggle a spare IO pin 10 times and see if the 640 nsecs grows accordingly. Between that and a scope probe on the timer output, you should be able to work out what’s going on.

Where exactly is that scope probe connected? A 200mV dip on Vref during conversions looks like a big problem to me. While it might be useful for determining when the ADCs start running, once that’s sorted you probably need to make those dips go away if you want accurate readings. You really want Vref to be totally noise free.

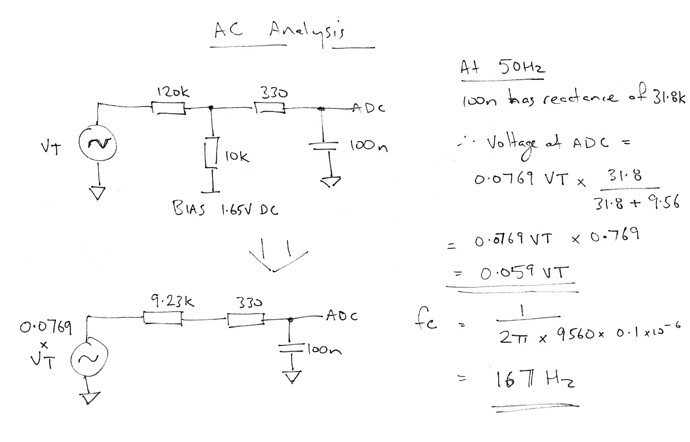

Can you run the two boards side by side, fed from the same VT? Then you could probe the two signals at the the ADC inputs and see if one is 25% larger. I just noticed in your schematic above you appear to have the same problem as described here (skip the first paragraph and start at “I wonder if your voltage divider and LPF are working the way you think they’re working”). Your Thevenin equivalent circuit looks something like:

So I suspect your cut-off frequency (167 Hz) is much lower than you were planning, and your divider is reducing the voltage more than you were planning (/17 instead of /13).

P.S. Sorry about the 19 day delay in responding… I only got notified of your post this morning.

P.P.S. That inadvertent savage cutoff frequency also means a massive phase shift of about 16.7°, while the phase shift of the I LPF is closer to about 0.6° so between them, the LPFs have added about a 16° net phase error… or about 0.9 msecs at 50 Hz.