Hello,

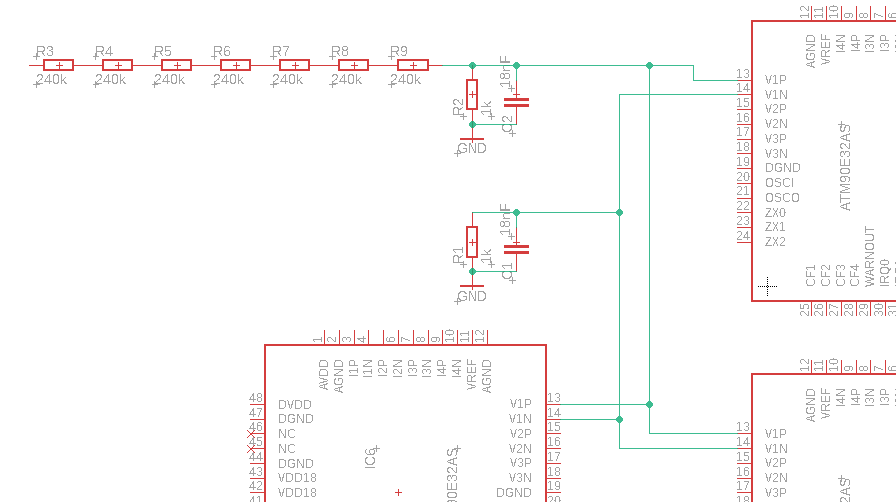

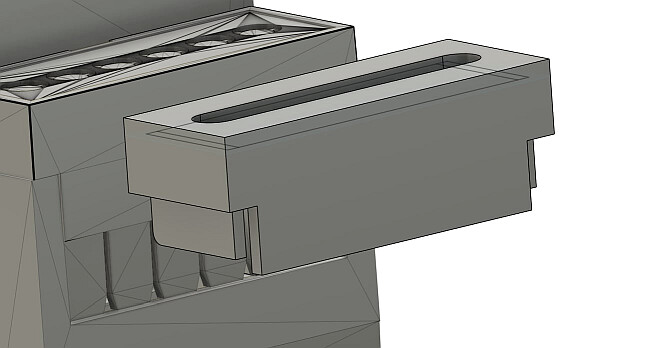

I’m currently developing my own DIN Rail Meter based on the Atmel ATM90E32 IC.

It should be 2 modules wide with 3 voltage and 9 current channels.

This is where I got my idea: GitHub - CircuitSetup/Expandable-6-Channel-ESP32-Energy-Meter: Hardware & Software documentation for the CircuitSetup Expandable 6 Channel ESP32 Energy Meter. Works with ESPHome and Home Assistant.

And this is my project: GitHub - denes44/DIN-Rail-Power-Meter

I would love to have a couple questions about the application of this IC if you can help me.

Voltage monitoring

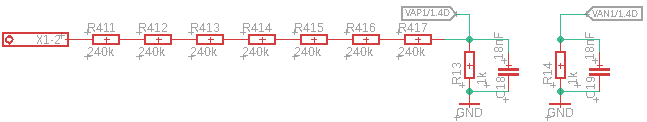

I decided to go with the resistor network from the application note to measure the voltage.

Mostly because of the size. And since the final device is meant to be installed inside the electrical cabinet and doesn’t have any outside interfaces, just the Wi-Fi I don’t think the lack of isolation will be a problem.

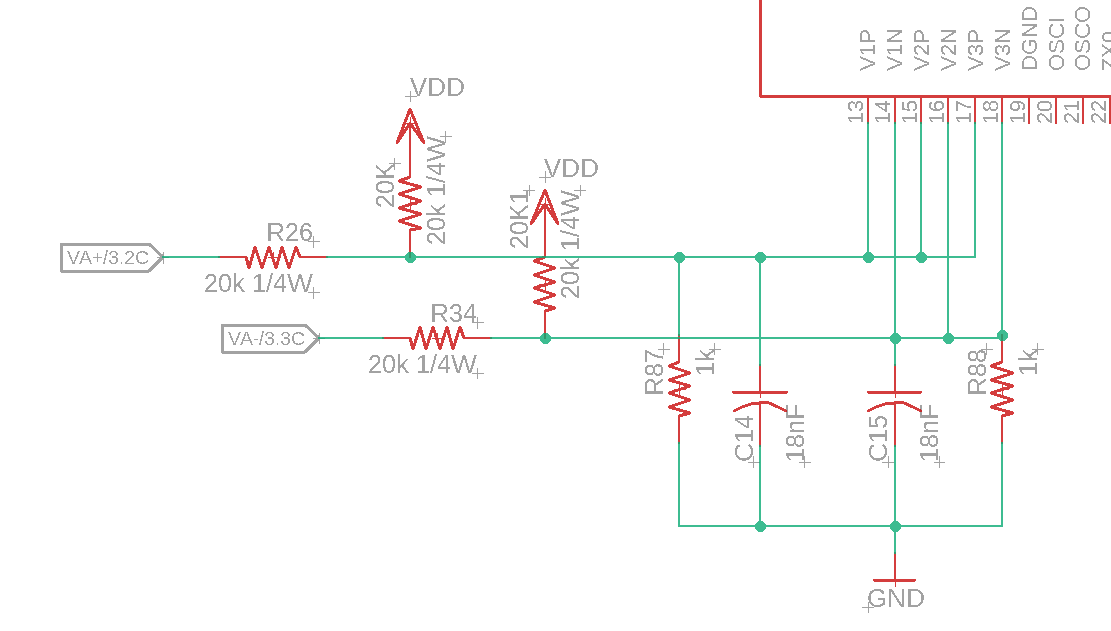

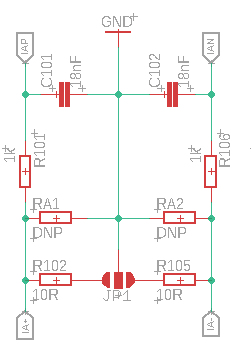

This is the voltage measuring circuit from the application note:

As far as I understand, this is “just” a voltage divider with a 1680k : 1k ratio.

Wouldn’t the resulting voltage be too small? The maximum the IC can take is 720 mVrms.

The second question is that the resistor size (1206) is because of the voltage rating, not because the power rating, right? I assume I’ll need some good resistors here with a high power rating like the HV06W series from Uni-royal, 500V max. working voltage, 1/4W power rating.

Multiple voltage monitoring for every IC

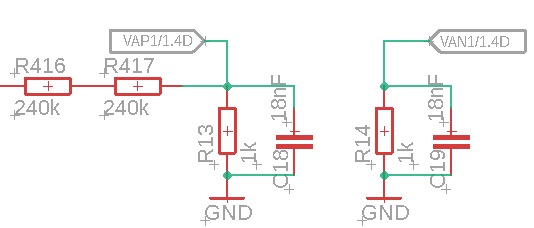

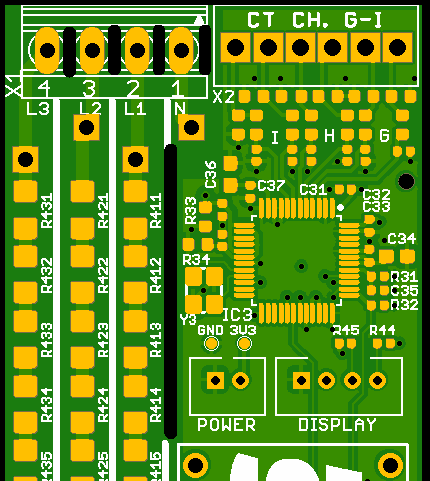

Right now the circuit is set up, that I have 3 ICs on the PCB, and each IC monitors the voltage of one phase.

So I have the output of the voltage divider connected to all three inputs of the IC:

Technically it isn’t necessary, because I can configure it by software use the V1 input for for all 3 current inputs, but it doesn’t hurt, and the original project does it this way too.

The problem with this if somebody only wants to measure the total current of each phase, still all 3 ICs are needed on the PCB, it’s not possible to use a version where there is only one IC is needed (thus cheaper).

The other disadvantage could be in a 3 phase environment is that each IC can measure currents on one specific phase, so it’s 3 current channels per phase, I cannot do for example 8-1-1.

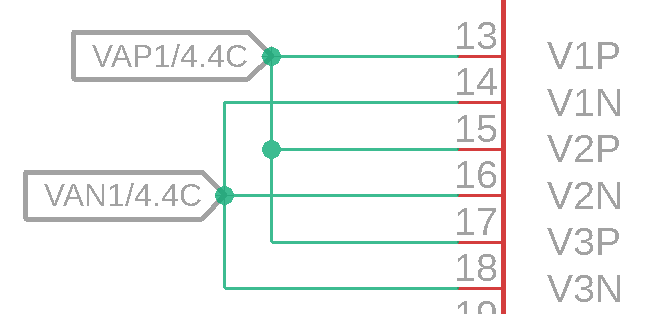

To overcome this, I plan to connect the 3 phases to every IC, so the L1 would be V1 on IC1,2,3; L2 would be V2 on IC1,2,3 and L3 would be V3 on IC1,2,3.

The question is do I need to duplicate any component to do this? Like a separate capacitor for every IC, or anything like this.

Or I can just connect the “output” of the voltage divider, VAP1, to the V1P input of all ICs parallel, like I do now with the V1-2-3 input on the same IC?

Circuit monitoring

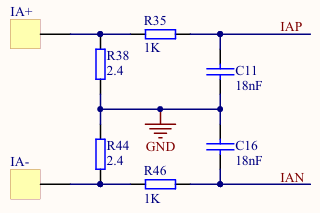

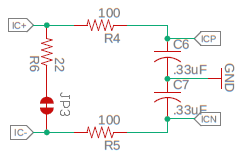

This is the current measuring circuit from the application note:

And this is from the github project:

There are two key differences, one is the value of the R4/5-R35/R46 and the C6/7-C11/16.

I assume these are just an RC low-pass filters, and doesn’t really modify the measurement value, right?

I tend to go with the values from the application note, but JLCPCB doesn’t have a 18nF capacitor as a basic part, so I’m planning to change it to 22nF. That shouldn’t make too much of a difference, right?

The other thing is the burden resistor. On the second circuit it’s clear that it’s R6.

On the first one I assume the R38 and R44 resistors are the burden resistors, but why they are connected this way, so the middle point is connected to GND?