It’s back to interpolation then.

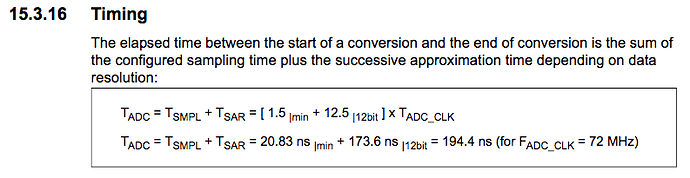

In the for loop, iterating over the DMA buffer, defining which indexes to correlate. The crucial bit of knowledge in this case is the time per ADC conversion. I don’t know this value, I know it’s not as simple as 601.5 cycles as defined in CubeMX.

. Sampling time.

. Conversion time.

. and?

Anyway, 0.000008354166667 usecs for 601.5 cycles at 72MHz. Correct?..

. https://www.st.com/content/ccc/resource/technical/document/reference_manual/4a/19/6e/18/9d/92/43/32/DM00043574.pdf/files/DM00043574.pdf/jcr:content/translations/en.DM00043574.pdf

RM0316 pages 322 and 325.

This is it. We can calculate the time represented between buffer indexes.

601.5 cycles with an ADC prescaler of 2 is used in the 3CT example.

A better calculation example then is:

601.5+12.5 x (1/(72,000,000/2))

16.70833347usecs + 0.347222225usec = 17.055555695usecs.

58.7kHz sampling rate.

978 samples per complete waveform at 60 Hz.

Can someone verify?

How does this translate into phase correction?

I derive 5kHz as sufficient based on 100 samples per 1/50Hz waveform. So 58kHz is great. Slowing this down significantly can be done if we need more CPU/memory resources.

Spotted this: ADS1115 and sampling speed - #2 by Robert.Wall

But do we need to define a strict sampling rate based on 50/60Hz if we have zero-crossing detection? Probably not.